发布时间:2023-08-29 来源:光子盒研究院

近日,来自两个研究小组的最新模拟报告称,一类新兴的量子纠错码的效率比目前的“黄金标准”(即表面码)高出一个数量级。

量子纠错码的工作原理都是将大量容易出错的量子比特转换成更小的“受保护”量子比特,这些量子比特很少出错。但在这两次模拟中,低密度奇偶校验码(LDPC码)可以用比表面码少10到15倍的原始量子比特生成受保护的量子比特。这两个研究小组都没有在实际硬件中实现这些模拟的飞跃,但实验表明,这些代码或类似的代码可以加速能力更强的量子设备的到来。

经典计算机依靠比特运行,很少发生误操作。但是,为量子计算机提供动力的粒子状物体——量子比特,一旦被任何东西从其量子态这一微妙状态中挤压出来,就会失去“量子魔力”。

为了让未来的量子比特发挥作用,研究人员计划使用量子纠错技术,即使用额外的量子比特对信息进行冗余编码。这种方法的原理类似于把每个单词说两遍,把信息分散到更多的字符中,从而保护信息不受静态干扰。

1998年,美国加州理工学院的Alexei Kitaev和俄罗斯朗道理论物理研究所的Sergey Bravyi推出了量子纠错表面码。

以往实验中,使用的距离-3表面码

它将量子比特组织成一个正方形网格,执行类似于扫雷的游戏:每个量子比特连接四个相邻的量子比特,因此检查指定的辅助量子比特就可以悄悄地窥探四个携带数据的量子比特。根据检查返回的是0还是1,科学家们可以推断是否有邻位出错;通过在电路板周围进行检查,科学家就可以推断出错误所在并进行修复。

通过这些检查,以及对有问题的量子比特进行更微妙的调整,还可以在方形块的数据携带量子比特中隐藏一个可靠的量子比特,不完全是这里或那里——而是到处都是。只要“可疑”量子比特能保证“扫雷”操作顺利进行,隐藏的量子比特就会保持安全,并能被操纵执行操作。通过这种方式,表面码优雅地将许多“低劣的”量子比特融合到一个很少出错的量子比特中。

一直以来,该代码都是量子纠错的黄金标准;它对行为不端的量子比特具有很高的容忍度,而且网格易于可视化。因此,表面码影响了量子处理器和量子路线图的设计。

表面码的缺点是对量子比特的“贪得无厌”:为了更有力地保护可靠的量子比特,需要更大的伪劣量子比特块。要制作多个受保护的量子比特,就需要将多个块拼接在一起;对于梦想在许多受保护量子比特上运行量子算法的研究人员来说,这些都是沉重的负担。

2013年,Gottesman看到了摆脱困境的可能途径。

包括Terhal和Bravyi在内的研究人员发现,有证据表明,对于只将相邻比特连接到相邻比特的平面代码来说,表面码的效果是我们所希望的;但是,如果允许每个校验将相距甚远的量子比特连接在一起呢?量子信息理论家们已经开始探索具有这种“非局域”连接的编码,这种编码被随意地称为LDPC码。(令人困惑的是,从技术上讲,表面码也是一种LDPC码;但在实践中,该术语通常指的是具有非本地校验的氏族成员)。

Gottesman随后证明,某些LDPC码可以不那么“贪婪”:它们可以将多个受保护的量子比特塞进一个块中,这将有助于避免表面码对较大算法的量子比特需求膨胀。

但Gottesman的研究是高度理想化的,考虑的基本上是无限的量子比特群。实际的挑战在于,研究人员能否缩小LDPC码的规模、使其适用于真正的量子设备,同时保持其强大的性能。

Nikolas Breuckmann多年来一直试图超越表面码——量子纠错的黄金标准,他认为LDPC码可能就是答案。

过去两年里,Breuckmann和其他研究人员开始仔细研究能在越来越小的系统上运行的LDPC代码的性能。他们希望一些LDPC码能够适合当今的设备:这些设备可以提供大约100个原始比特。

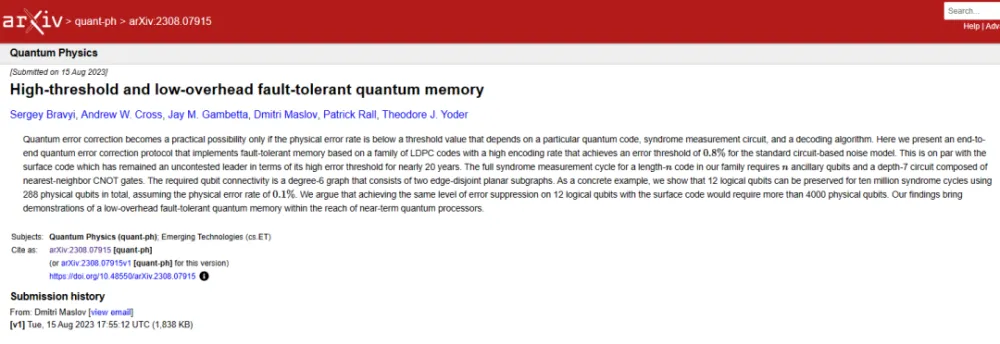

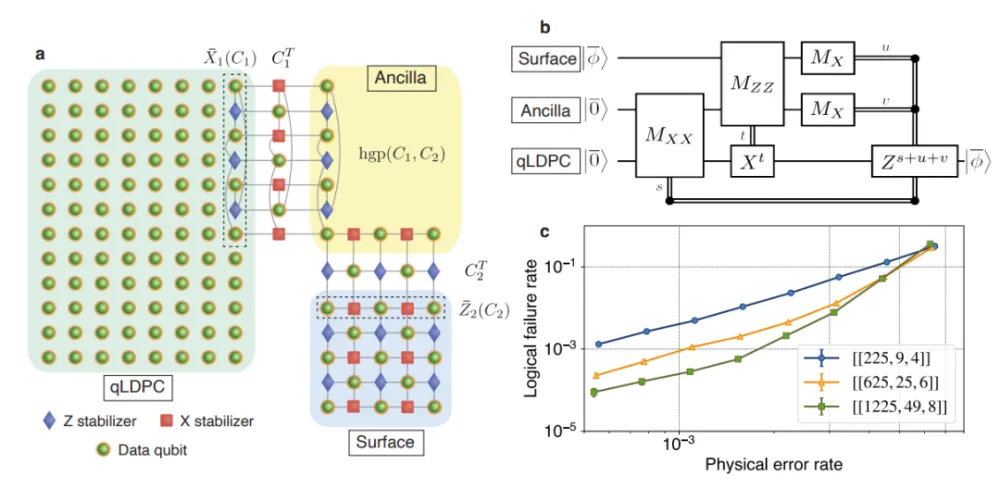

上周,由Breuckmann领导的IBM研究团队根据2012年发表的一篇鲜为人知的论文中的LDPC代码,模拟出了迄今为止最小、最具体的LDPC蓝图。它从表面码的四个相邻量子比特校验开始,添加了两个精心挑选的“非局域”量子比特。

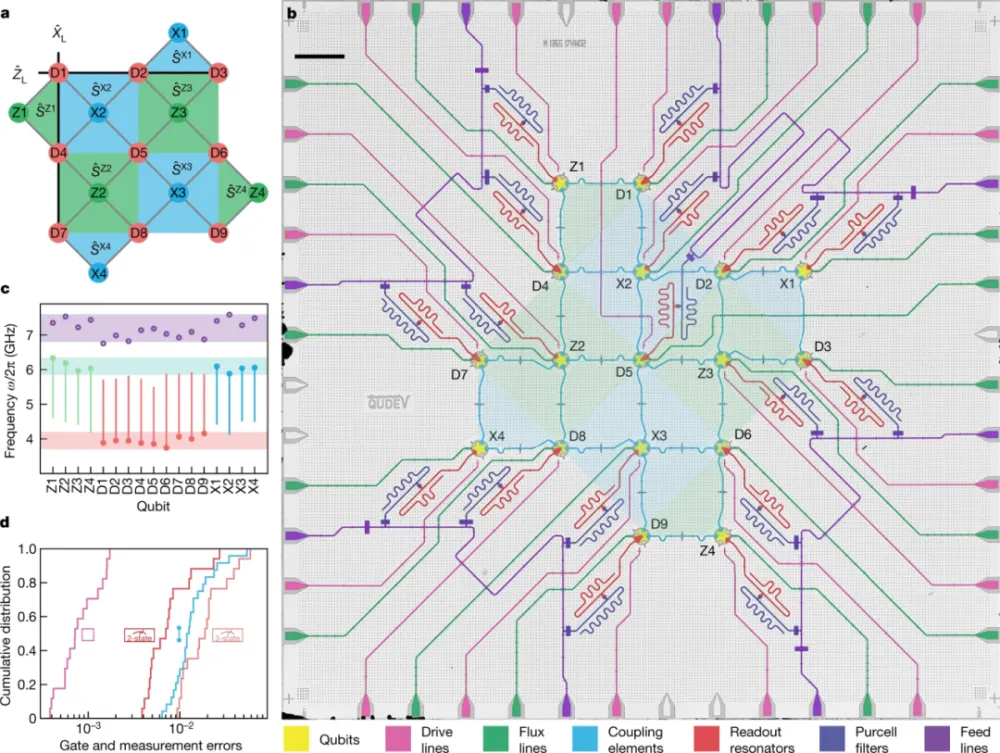

准循环LDPC码的小型实例及其基于电路噪声模型的性能。

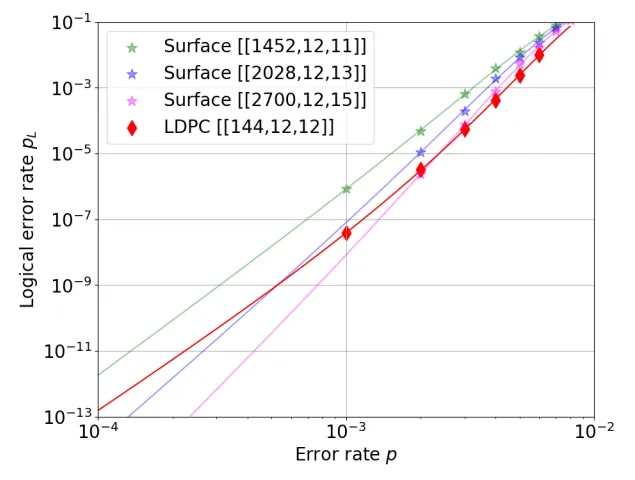

准循环LDPC码[[144,12,12]]与具有12个逻辑量子比特和距离d∈的表面码的比较。具有12个逻辑量子比特的距离-d表面码长度为n=12d^2,因为每个逻辑量子比特都被编码到表面码网格的一个单独的d×d片段中。图中显示了通过对距离-d代码执行d个综合征循环估算出的逻辑错误率pL。由于采样误差,大部分数据点的误差条≈pL/10。

预印本链接:

https://arxiv.org/abs/2308.07915

他们模拟了在真实电路上运行该代码时可能出现的各种错误,这一过程就像把数字战斗机放入数字风洞,看看它是如何飞行的。他们发现,与表面码相比,他们的代码能更有效地保护其可靠的量子比特。在一次测试运行中,该代码提取了288个故障率为0.1%的原始量子比特,并利用它们创建了12个受保护的量子比特,故障率降低了1万倍。据研究小组估计,对于同样的任务,表面码需要超过4000个输入量子比特。

IBM团队的研究员Andrew Cross说:“我们对此感到非常惊讶。”

这一模拟预示着今天就能实现未来的纠错功能:因为虽然没有人能够获得4000个量子比特,但拥有数百个量子比特的设备却指日可待。

Gottesman评论道:“你可以看到,与我们今天拥有的量子比特数量相当的设备具有相当大的容错能力。”

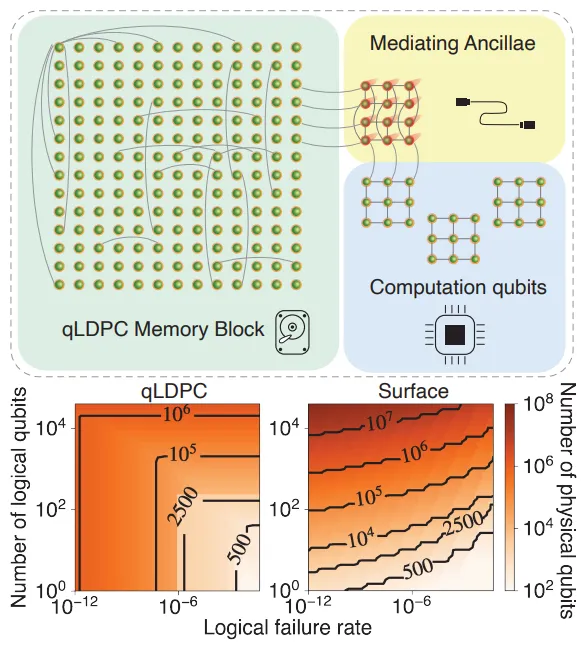

IBM的预印本发表一天后,以哈佛大学的Mikhail Lukin和芝加哥大学的蒋良为首的多机构合作研究人员也公布了类似的结果。他们对另外两种LDPC代码进行了清理,并对它们进行了仿真修改,结果发现,与表面码相比,这两种代码也只需要大约十分之一的输入比特数,就能生成几十到几百个好的比特。

预印版链接:

https://arxiv.org/abs/2308.08648

但是,制造一架F-35战斗机比模拟一架F-35战斗机更难,而制造一个可使用LDPC代码的设备也将极具挑战性。Gottesman解释表示,有两件主要的事情可能会阻止这些东西的实际应用:

-首先,在量子比特之间建立非局域连接非常困难,尤其是对于像IBM这样用固定超导电路制造量子比特的公司来说。将这些电路与它们的“邻居”连接起来是很自然的事,但在遥远的量子比特之间建立联系却并非如此。

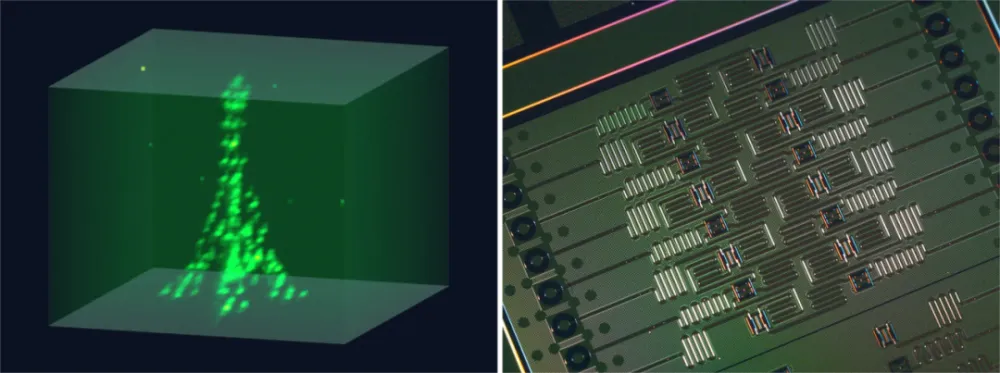

对于依赖移动量子比特的系统来说,将相距甚远的量子比特连接在一起可能更容易,比如2018年一个团队用来组装这座原子埃菲尔铁塔(左)的自由漫游原子。对于使用静态量子比特的系统(如IBM芯片中的16个超导量子比特(右图))来说,这将是一个更大的挑战。

-其次,当受保护的量子比特被用于存储时,LDPC码就会表现出色——就像在IBM的模拟中那样。但在使用这些模糊、重叠的量子比特进行计算时,纠缠不清的非局域代码结构使得选择和引导所需的量子比特变得更加困难。

Gottesman认为,“原则上是有可能完成这些计算的,但我们不知道是否有可能以真正实用的方式做到这一点。”

新的实验中,Lukin及其同事在解决这些主要缺陷方面迈出了微小的步伐。首先,研究小组通过将LDPC保护的量子存储器与表面码保护的量子处理器结合起来,模拟了端到端的计算。在该方案中,量子比特的节省在很大程度上减轻了计算负担,但代价是计算运行时间更长。

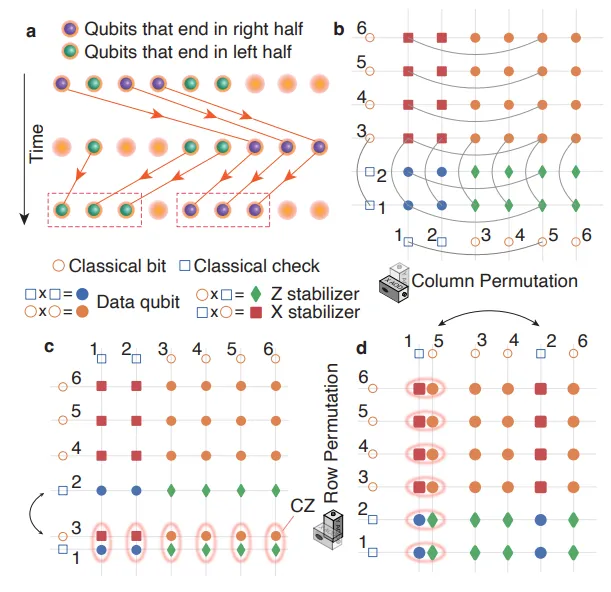

此外,Lukin团队还针对一种自由漫游量子比特进行了量身定制的模拟,这种量子比特非常适合安排长距离连接。与静止的超导电路不同,他们的量子比特是由激光束固定的原子。通过移动激光器,他们可以让遥远的量子比特接触——这对LDPC码来说非常重要。

使用可重构原子阵列的基于qLDPC的容错量子计算机体系结构。

用原子阵列高效实现量子LDPC码。

qLDPC存储器性能

从表面码到qLDPC码的容错隐形传态。

事实上,LDPC码何时甚至能否实用化仍不确定。即使是最乐观的预测,数十个可靠的存储比特的演示也可能至少需要几年的时间,而计算仍然遥遥无期。但最近的模拟使表面码看起来越来越像量子计算道路上的垫脚石,而不是终点。

“表面码存在20年是有原因的。”参与此次实验的研究人员表示,“它很难被打败,但现在我们有证据表明,我们确实可以打败它。”

参考链接:

[1]https://arxiv.org/abs/2308.03750

[2]https://journals.aps.org/prl/abstract/10.1103/PhysRevLett.129.050504

[3]https://pme.uchicago.edu/faculty/liang-jiang

[4]https://www.quantamagazine.org/new-codes-could-make-quantum-computing-10-times-more-efficient-20230825/

[5]https://research.ibm.com/blog/error-correction-codes